# Design an Ultra Wideband Low Noise Amplifier at 6 GHz Applications

Jitendra Mishra, P.K.Paul

Department of ECE, NIT, Silchar, India. E-mail: jeetu.er@gmail.com Department of ECE, NIT, Silchar, India. E-mail: pkp059@gmail.com

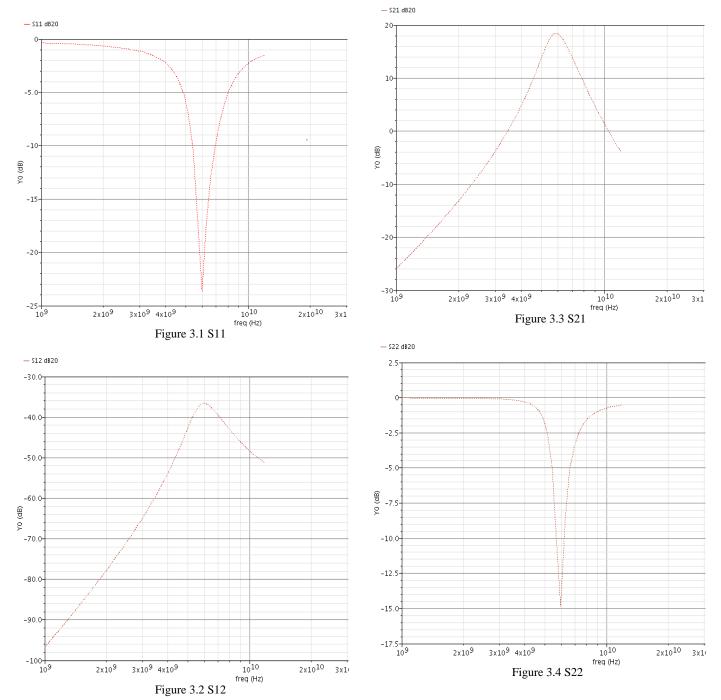

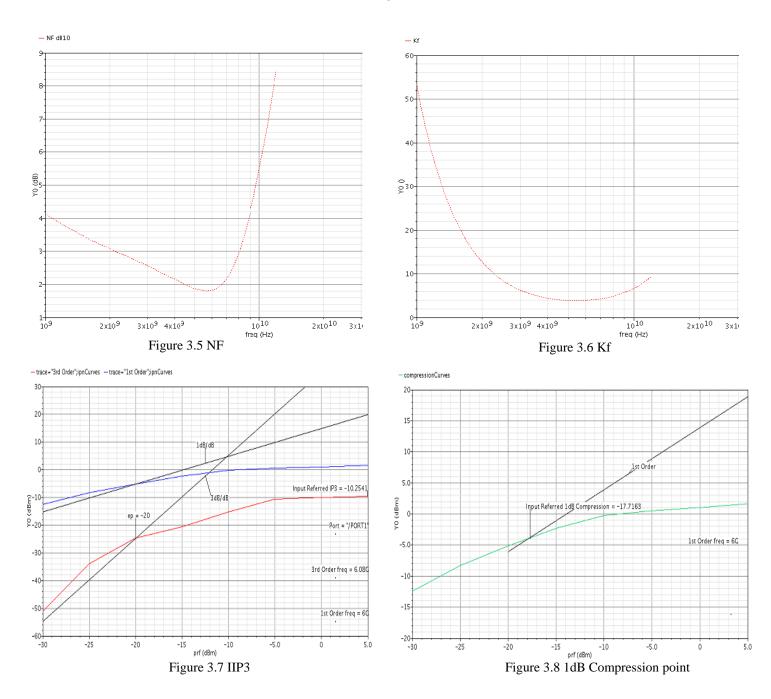

*Abstract*—This paper presents a ultra wideband low noise amplifier for 6GHz Applications. This proposed LNA is the extension of inductively common source amplifier and in this design we used transistor multifingering techniques in order to reduce noise and improves gain. This LNA is simulated by using UMC .18um CMOS mixed signal/RF process in cadence virtuoso. In this design, used current source biasing, with power supply is 1.8v. LNA achieved gain 19dB and noise figure is 1.8dB at operating frequency range, and input & output return losses are -24dB & -15dB respectively, reverse isolation is -36dB and stability is 4, IIP3 is -10dBm, 1-dB compression point -17dBm and total power consumption is 9mw.

**Keywords**—cascode source degeneration amplifier, current mirror, low noise amplifier, de-Q resistor, multifingring Techniques.

### I. INTRODUCTION

Ultra wideband communication system is a new wireless communication system that transmits an extremely low signal power over an ultra bandwidth [1]. It has an ability to provide high data rate at low cost with relatively low power. In the wireless communication system, low noise amplifier is the first block in the receiver, so that the sensitivity and noise figure of receiver is highly depend upon the gain and noise figure of low noise amplifier, and overall performance of receiver is depend upon low noise amplifier, the design of the front end low noise amplifier is one the challenges in radio frequency (RF) receivers, which needs to provide good input impedance matching, enough power gain and low noise figure (NF) with the operating frequency range. Various CMOS UWB LNA design techniques had been reported for wideband communication application. The well -developed distributed amplifier provides impedance matching, flat gain over wide bandwidth, but they are power hungry and occupy large area for the use of on chip transmission line [2, 3]. The resistiveshunt feedback amplifiers provide wideband input matching, low noise figure using loop gain [4], but they are require large power to achieve a high loop gain in single stage. A common amplifier has the highest potential to achieve the gate wideband input matching, good linearity and input and output isolation, but it leads to lower gain and higher noise figure(NF) [5]. In this paper, a low noise amplifier for ultra wideband application was designed using .18um CMOS technology based on cascode source degeneration topology, in this design for reducing noise figure we used parallel combination of two NMOS transistor at output, and used a d-Q resistor parallel to drain inductor for stability purpose, so by using this techniques

we got gain 19dB, noise figure 1.8dB, input and output return losses are -24dB & -15dB respectively, reverse isolation is - 36dB and stability factor is 4, and power consumption is 9mw.

# II. CIRCUIT DESIGN AND ANALYSIS

In the design of low noise amplifier there is tradeoff between different parameters i.e. gain, noise figure, power consumption, linearity, bandwidth, impedance matching, if we goes to improves some parameters, other parameter can be disturbed. So here my objective is to achieve higher gain with minimum noise figure.

# Noise figure (NF)

According to friss formula overall noise figure of n-stage receiver is-

$$NF_{tot} = 1 + (NF_1 - 1) + \frac{(NF_2 - 1)}{A_1} + \cdots \frac{(NF_n - 1)}{A_1 \dots \dots A_{(n-1)}}$$

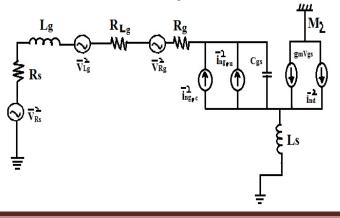

Here  $A_1$  is the gain of first stage and it is usually high, we can discard the noise contribution of the later stages on overall noise calculation, that is why we concentrates only on the noise of M1, which is shown in fig.1.

Jitendra Mishra, IJECS Volume 05 Issue 08 Aug 2016 Page No.17506-17510

Figure 1

The noise figure is the ratio between the total output noise power due to all noise sources and the output noise power generated by the input source [5]. The input stage of M1

$$NF = \frac{\overline{V_{Rs}^{2}} + \overline{V_{Rg}^{2}} + \overline{V_{Lg}^{2}} + \overline{V_{Lg}^{2}}}{\overline{V_{Rs}^{2}}}$$

It contains current noise in drain  $(\overline{u_{nd}}^2)$ , current noise in gate  $(\overline{\iota_{ng}^2} = \overline{\iota_{ng,c}^2} + \overline{\iota_{ng,u}^2})$ , resistance noise from  $R_g$  and  $L_g$   $(\overline{\iota_{Rg}^2})$ and  $l_{Lg}^2$  ). Here we are using power constrained noise optimization techniques this gives a specified bound on power consumption, this method then yield the optimum width that minimizes noise. So the noise figure of such device is:-

$$NF = 1 + \frac{R_{Lg}}{R_s} + \frac{R_g}{R_s} + \frac{\gamma \chi}{\chi Q_L} (\frac{\omega_0}{\omega_T})^2$$

$\gamma$  Is the thermal noise in the channel of M1,  $\alpha = \frac{g_{m1}}{g_{d01}}$  ( $\alpha = 1$  in long channel device),  $Q_L$  is the quality factor of input match network and equal to  $\frac{1}{\omega_0 R_S C_{gs1}}$ ,  $\omega_0$  is the operating frequency and  $\omega_T = \frac{g_{m1}}{c_{as1}}$  is the unity gain frequency.

Optimum Value of Q<sub>L</sub> for power constrained noise optimization:

$$Q_{L,opt,pd} = |C| \sqrt{\frac{5\gamma}{\delta}} \left[ 1 + \sqrt{1 + \frac{3}{|c|^2} (1 + \frac{\delta}{5\gamma})} \right] \approx 3.9$$

So, minimum noise figure is-

$$NF_{min,pd} \approx 1 + 2.4 \frac{\gamma}{\alpha} (\frac{\omega_0}{\omega_T})$$

#### Input impedance match

From the fig. 1 the input impedance of LNA is  $Z_{in} = sL_g + R_{Lg} + R_g + sL_s + \frac{1}{sC_{gs1}} + \omega_T L_s$ , we can equal these input impedance to source impedance of  $50\Omega$ , for the simplification neglect the value of  $R_{Lg}$  and  $R_g$ , then  $\omega_T L_s = R_s \rightarrow L_s = \frac{R_s}{\omega_T}$  $L_g = \frac{1}{\omega_0^2 C_{gs1}} - L_s$ and

#### Gain

In low noise amplifier there is a several types of gain i.e. operating power gain, transducer power gain, and available power gain. Operating power gain  $G_P$  is the ratio of power delivered to the load to power supplied to amplifier, transducer power  $gain G_T$  is the ratio of maximum power available from source to power delivered to load;

Available power gain  $G_A$  is the ratio of power available from the source to power available from the amplifier

$$G_{p} = \frac{1}{1 - |\Gamma_{in}|^{2}} |S_{21}|^{2} \frac{1 - |\Gamma_{L}|^{2}}{|1 - S_{22}\Gamma_{L}|^{2}}$$

$$G_{T} = \frac{|S_{21}|^{2} (1 - |\Gamma_{S}|^{2}) (1 - |\Gamma_{L}|^{2})}{|(1 - S_{11}\Gamma_{S}) (1 - S_{22}\Gamma_{L}) - (S_{12}S_{21}\Gamma_{S}\Gamma_{L})|^{2}}$$

$$G_{A} = \frac{1 - |S_{11}|^{2}}{|1 - S_{11}\Gamma_{S}|^{2}} |S_{21}|^{2} \frac{1}{|1 - S_{22}\Gamma_{L}|^{2}}$$

$\Gamma_{in}$  Represents the input reflection coefficient,  $\Gamma_{S}$  represents the source reflection coefficient,  $\Gamma_L$  represents load reflection coefficient.

#### **Circuit design**

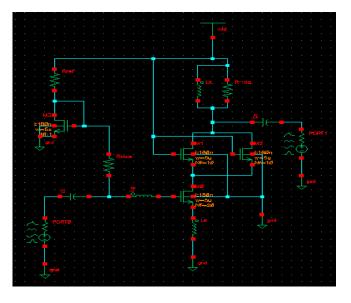

The overall performance of the low noise amplifier is determined by calculating the transducer gain, noise figure and input and output reflection coefficients. The complete schematic design of low noise amplifier is shown in figure 2. Transistor M1 is common source degeneration amplifier and M2, M3 are common gate amplifier, by using these cascode network reverse isolation is improved, Cinis the input dc blocking capacitor,  $C_o$  is output blocking capacitor,  $L_S$  is source degeneration inductor is used to give the input matching and high input impedance,  $L_g$  is gate inductor used to tune out the effect of C<sub>in</sub> and set the resonant frequency, L<sub>d</sub> is drain inductor used to tuned the output and increase gain and also work as a band pass filter form with Co. Rd resistance is d-Q resistor are connected parallel to drain inductor in order to increase stability. R<sub>ref</sub> and R<sub>bias</sub> is the part of biasing network. The calculated width of M1 is 130um but we chosen width of M1 is 100um, M2=M3 is 50um and M5 is 5um. The components values are given in table 1. Here inductor Lg, Lsand Ld are on chip spiral inductor.

Proposed Circuit of LNA: This schematic circuit is designed by using cadence tool.

Figure: 2 Schematic Diagram of LNA

# DOI: 10.18535/ijecs/v5i8.13

The values of the components are-

| Components | Lg     | Ls    | Ld    | Rbias | Rref | Cin | Cout  | Rs  | Vdd  |

|------------|--------|-------|-------|-------|------|-----|-------|-----|------|

| Value      | 3.39nH | 200pH | 2.8nH | 2.4K  | 2.4K | 2pF | 130fF | 50Ω | 1.8v |

| Table.1    |        |       |       |       |      |     |       | •   |      |

RESULT TABLE

| Frequency | S <sub>11</sub> (dB) | S <sub>12</sub> (dB) | S <sub>21</sub> (dB) | S <sub>22</sub> (dB) | NF(dB) | K <sub>f</sub> | IIP3(dBm) | 1 dB        |  |  |

|-----------|----------------------|----------------------|----------------------|----------------------|--------|----------------|-----------|-------------|--|--|

| (GHz)     |                      |                      |                      |                      |        |                |           | Compression |  |  |

|           |                      |                      |                      |                      |        |                |           | point(dBm)  |  |  |

| 6         | 24                   | -36                  | 18.53                | -15                  | 1.8    | 4              | -10.25    | -17.7       |  |  |

|           |                      |                      |                      |                      |        |                |           |             |  |  |

| Table 2   |                      |                      |                      |                      |        |                |           |             |  |  |

# III. CONCLUSION

As we know low noise amplifier is the crucial part in RF receiver. In this paper design the low noise amplifier at 6GHz operating frequency, it has stimulated by using cadence for this design and it offers improved gain, good reverse isolation and reduced miller effect, this LNA recorded the

Virtuoso tool by using .18um CMOS Technology, we have chosen cascode topology with source degeneration

# DOI: 10.18535/ijecs/v5i8.13

amplifier gain  $S_{21}$  is 18.53dB and the return loss  $S_{11}$  and  $S_{22}$  is -24dB and -15dB, reverse isolation is -36dB noise figure is 1.8dB, stability factor  $K_f$  is 4, power consumption is 9mw.

#### REFERENCE

- [1] S Stroh, "Ultra-wideband: Multimedia unplugged", *IEEE spectrum* vol.40, pp. 23-27, sep. 2003.

- [2] Kuan-Hung Chen and Chorng-Kuang Wang, "A 3.110.6GHz CMOS cascaded two-stage distributed amplifier for ultra-and applications," *Advanced Systems Integrated Circuits 2004, Proceedings of 2004IEEE Asia-Pacific Conference on 4-5 Aug.2004, pp.296-299.*

- [3] Chen, K. H., J. H. Lu, B. J. Chen, and S. L. Liu, "An Ultra-wideband 0.4-10GHz LNA in .18um CMOS," *IEEE Transactions on Circuits and system II: Express Briefs, vol. 54, No.3, 217-221.*

- [4] Chang-Hsi Wu and Yu-Po Lin, "A Low-Power CMOS Low Noise, amplifier for UWB Applications", *ICUB2010, 20-23 Sept. 2010.*

- [5] A. Bevilacqua and A. Niknejad, "An ultra wideband CMOS LNA for 3.1-10.6GHz wireless receivers," *IEEE Journal of solid-state circuits*, vol 39, pp. 2259-2268

- [6] D. Shaeffer and T. Lee, "A 1.5v 1.5 GHz CMOS Low Noise Amplifier," JSSC, May 1997.

- [7] Jon Guerber, "Design of a 2.4GHz CMOS Low noise Amplifier", 2010.

- [8] T. Lee, "The Design of radio frequency integrated circuits," second edition, publishing house of electronics industry 2006.

- [9] BehzadRazavi, "Design of Analog CMOS Integrated Circuits", New York: McGraw-Hill, 2001

- [10] Bosco Leung ,"VLSI for wireless communication"