# Design and Implementation of AMBA-AHB&APB bridge memory controller by VHDL

S.Anoosh<sup>1</sup> T.Vidhya<sup>2</sup> B.Vinod Kumar<sup>3</sup> Ch.Anitha<sup>4</sup> S.Rama Krishna<sup>a</sup>

anoosh.santosh@gmail.com vidhya.taddi@gmail.com badireddiv@gmail.com ch.anitha1111@gmail.com slkrishna444@gmail.com

<sup>1234</sup> Student, Department of ECE, Lendi Institute of Engineering and Technology, Vizianagaram, India.

<sup>a</sup> Assistant Professor, Department of ECE, Lendi Institute of Engineering and Technology, Vizianagaram,

India.

Abstract-Microprocessor performance has improved rapidly these years. In contrast, memory latencies and bandwidths have improved little. The result is that the memory access time has been a bottleneck which limits the system Memory controller (MC) performance. is designed and built to attacking this problem. The memory controller is the part of the system that, well, controls the memory. The memory controller is normally integrated into the system chipset. This paper shows how to build an Advanced Microcontroller Bus Architecture (AMBA) compliant MC as an Advanced Highperformance Bus (AHB) slave. The MC is designed for system memory control with the main memory consisting of SRAM and ROM. Additionally, the problems met in the design process are discussed and the solutions are given in the paper.

# Keywords - ARM; AMBA; Memory Controller; AHB&APB bus

## I. INTRODUCTION

With the improvement of Microprocessor these years, the memory access time has been a bottleneck which limits the system performance. Memory controller (MC) is designed and built to attacking this problem. The memory controller is the part of the system that, well, controls the memory. It generates the necessary signals to control the reading and writing of information from and to the memory, and interfaces the memory with the other major parts of the system. The memory controller is normally integrated into the system chipset. In this paper, an Advanced Microcontroller Bus Architecture (AMBA) compliant memory controller is designed for system memory control with the main memory consisting of SRAM and ROM. The memory controller is compatible with Advanced High-performance Bus (AHB) which is a new generation of AMBA bus, so we call it "AHB-MC". The AHB-MC has several features which are shown as follows

1.Designed with synthesizable HDL for Application Specific Integrated Circuit (ASIC) synthesis

2.Supports multiple memory devices including static random access memory (SRAM), read-only

memory (ROM)

3. Complies with AMBA AHB protocol

4. Supports one to four memory banks for SRAM and ROM

5.Programmable memory timing register and configuration registers

6. Shared data path between memory devices to reduce pin count

7. Asynchronous FIFO to support burst transaction up to 16-beats This paper describes how to build the AHB-MC. And combining the problem met in the process of designing, the corresponding solutions are presented. Finally, the simulation results are presented.

# II. ARCHITECTURE OF AHB-MC

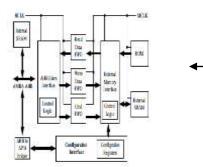

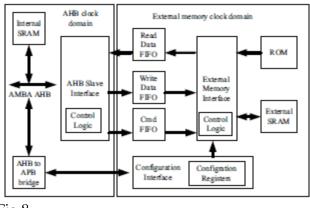

The AHB-MC mainly consists of three modules: AHB slave interface, configuration interface, and external memory interface [1]. Figure 1 shows the architecture of AHB-MC.

# A. AHB slave interface

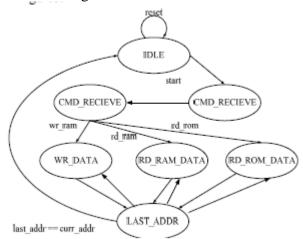

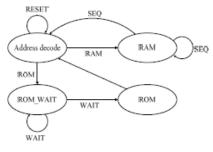

The AHB slave interface converts the incoming AHB transfers to the protocol used internally by the AHB-MC. The state machine is shown in Figure 2.

#### B. External memory interface

The external memory issues commands to the memory from the command FIFO, and controls the cycle timings of these commands. The state machine is shown in Figure 3.

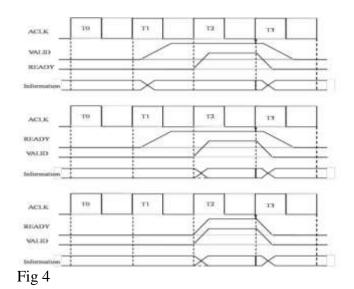

the timing of a read from memory and a write to memory with two wait states [2]. Memory read with two wait states Memory write with two wait states *Memory bank select*

Figure 4 shows system will change the memory map after system boot, AHB-MC is designed to support a remap signal which is used to provide a different memory map. AHB-MC has four memory banks, which are selected by XCSN signal. The XCSN signal is controlled by the address of a valid transfer, and the system memory map mode. So before the system memory is remapped, the boot ROM at 0x3000 0000 is also mapped to the base address of 0x0000 0000.

# 1. Memory write control

To support for writing in word (32-bits), half-word (16-bits) and byte (8-bits), the XWEN signal is used in the AHB-MC.

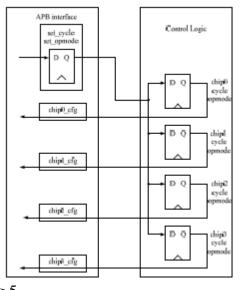

# Configuration interface

The main function of the configuration interface is to change the configuration registers (SETCYCLE and SETOPMODE register) according to the commands from AHB to APB bridge which converts AHB transfers from the configuration port to the APB transfers that the configuration interface require [3]. Each memory chip supported by AHB-MC has two registers (CYCLE register and OPMODE register), which contain all the timing parameters that are required for the controller to set correct access timings. Which cycle and operation mode registers are updated is determined by the configuration registers: **SETCYCLE** and

5

fig

as

#### Fig 5

## III. BURST TRANSFER SUPPORT

With the increasing system frequency, it's hard to accomplish the address decoding and memory access operations in one clock cycle. Therefore, wait states are inserted into the data cycle to ensure there is enough time for address decoding and memory accessing. But the method that inserting wait state will cause system performance drop dramatically. Therefore, a sequential-access (burst) method is presented to resolve this problem in this paper. In this method, all AHB fixed length burst types are directly translated to fixed length bursts, and all undefined length INCR bursts are converted to INCR4 bursts. Burst operation has performance benefits because when the first beat of a burst is accepted, it contains data about the remaining beats. For example, when AHB-MC got the first beat of a read burst, all the data required to complete the transfer can be read from memory and restored in the read data FIFO. SO this first transfer has some delay before data is returned. But subsequent beats of the burst can have less delay because the data they require might have already been prepared in the FIFO. To further improve the system performance, a RETRY response is used that AHB-MC can release the bus when it is preparing the data [4]. This mechanism allows the transfer to finish on the bus and therefore allows a higher-priority master to get access to the bus. The state machine is showed in figure 6.

Fig 6

#### IV. MEMORY SYSTEM

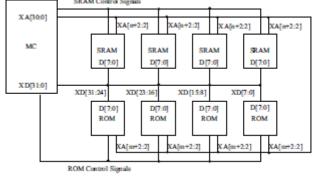

In the arm architecture, instructions are all 32-bits, while instructions are 8-bits in the external ROM and SRAM. Therefore the lowest two addresses of ROM and SRAM are not connected to the external address bus. Additionally, to support byte writing, SRAM needs to be separated as four independent banks or has a byte-write enable signal. The basic memory system architecture is shown in Figure 7.

#### V. ASYNCHRONOUS CLOCK

The AHB-MC has two clock domains: AHB clock domain and external memory clock domain as shown in Figure 8. Asynchronous FIFO is used between two clock domains as a data buffer.

The main benefit of asynchronous clocking is that you can maximize the system performance, while running the memory interface at a fixed system frequency. Additionally, in sleep-mode situations when the system is not required to do much work, you can lower the frequency to reduce power consumption [5]. However, asynchronous clock will cause the flip-flop going meta stable state and not converging to a legal stable state by the time the output must be sampled again as shown in Figure 8. To resolve this problem, the most common way is inserting a two-flip-flop synchronizer as shown in Figure 8.

# VI. VERIFICATION AND SIMULATION RESULTS

The verification method used in this paper, is to put the AHB-MC into a minimum system which consists of ARM core, AHB bus, APB bus and AHB-MC The code used for testing is put in ROM, if the system can work correctly, then we know the test case past. The simulation waveforms of a simple test code are shown. Figure 10 shows read with zero wait states form the

external ROM. The address is registered at rising edge of hclk (AHB bus clock), after which ex\_oen (external memory read enable) signal goes high, then read data reach hrdata (AHB read data bus) at falling edge of hclk. Fig Write with zero states to the external RAM is

# Fig 10

shown in Figure A write operation is initiated by hwrite going high. Then the address is send to external memory address bus and ex\_wen (external memory write enable) signal goes low to enable the data from hwdata (AHB write data bus) stored in the RAM fig10.

#### VII CONCLUSION

From this project we have successfully avoid the bottle-neck problem in microprocessors by using AMBA architecture – AHB & APB Bus. This project shows how to build an Advanced Microcontroller Bus Architecture (AMBA) compliant MC as an Advanced High-performance Bus (AHB) slave. The MC is designed for system memory control with the main memory consisting of SRAM and ROM. This can be implemented to 64bit but we have much bus bridge complexity.

#### REFERENCES

[1] "AMBA Specification (Rev2.0)", ARM Inc.

[2] "Prime Cell AHB SRAM/NOR Memory Controller", Technical Reference Manual, ARM Inc.[3] "AHB Example AMBA System", Technical Reference Manual, ARM Inc.

[4] Carter, J.; Hsieh,W., "Impulse: building a smarter memory controller", High-Performance Computer Architecture, Dept. of Comput. Sci., Utah Univ., Salt Lake City, UT.

[5] Clifford E. Cummings, "Synthesis and scripting Techniques for Designing Multi-Asynchronous Clock Designs", Sunburst Design, Inc